# CHAPTER 10

## **INPUT FUNCTIONS**

#### In This Chapter...

| Input Memory Mapping for Counter Data Transfer      | 10–2  |

|-----------------------------------------------------|-------|

| Input Memory Map for Scaled Counter Data            | 10–5  |

| Input Memory Map for Capture Count Data Transfers   | 10–9  |

| Input Memory Map for Edge Timer and Dual Edge Timer | 10–12 |

| Inhibit                                             | 10–22 |

| Input Memory Map for Pulse Catch Data Transfers     | 10–25 |

#### **Input Memory Mapping for Counter Data Transfer**

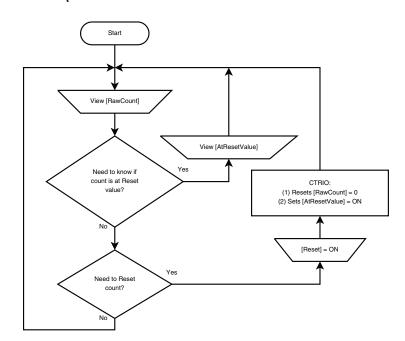

The Counter function is used to create counts from an attached encoder. To use this function, one input needs to be configured as a Counter or Quad Counter.

The following table shows which memory locations are used for memory transfers from the CTRIO(2) module to the CPU. The starting memory location is defined by the user in the I/O Map within CTRIO Workbench. For the *Direct*LOGIC CPU, memory address offsets are in the second column. When using H2-WinPLC, EBC, PBC, MODBUS, or DEVNETS CPUs in the CPU slot, use the non-PLC offsets in column one.

The proper sequence of events for using this function can be found in the flow charts shown in later pages following.

| Data Type and Offset<br>WinPLC, EBC, PBC,<br>DEVNETS, MODBUS | Address for Inputs<br>( <i>Direct</i> LOGIC) | Definition                                                                                         | Format | Bytes |

|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-------|

| dwX0                                                         | n+0                                          | Ch 1/Fn 1 Parameter 1                                                                              |        |       |

| dwX1                                                         | n+2                                          | Ch 1/Fn 1 Parameter 2                                                                              |        |       |

| dwX2                                                         | n+4                                          | Ch 1/Fn 2 Parameter 1                                                                              |        |       |

| dwX3                                                         | n+6                                          | Ch 1/Fn 2 Parameter 2                                                                              | DWord  | 4     |

| dwX4                                                         | n+10                                         | Ch 2/Fn 1 Parameter 1                                                                              | Dvvoia | 4     |

| dwX5                                                         | n+12                                         | Ch 2/Fn 1 Parameter 2                                                                              |        |       |

| dwX6                                                         | n+14                                         | Ch 2/Fn 2 Parameter 1                                                                              |        |       |

| dwX7                                                         | n+16                                         | Ch 2/Fn 2 Parameter 2                                                                              |        |       |

| bX07<br>bX815                                                | n+20                                         | Ch 1/Fn 1 Status (Low Byte)<br>Ch 1/Fn 2 Status (High Byte)                                        |        |       |

| bX1623<br>bX2431                                             | n+21                                         | Ch 2/Fn 1 Status (Low Byte)<br>Ch 2/Fn 2 Status (High Byte)                                        | Word   | 0     |

| bX3239<br>bX4047                                             | n+22                                         | Output 0 Status (Low Byte)<br>Output 1 Status (High Byte)                                          | vvord  | 2     |

| bX4855<br>bX5663                                             | n+23                                         | Output 2 Status (Low Byte)<br>Output 3 Status (High Byte)                                          |        |       |

| bX6471<br>bX7279<br>bX8087<br>bX8895                         | n+24                                         | System Functions<br>Read/Write CTRIO(2) Internal<br>Registers (see p. 6-10 for bit<br>definitions) | DWord  | 4     |

44 Total Bytes

#### Example Input Control/Status Bits and Parameter Register Addresses

The following tables provide example addresses based on V2000 selected for the base input address. The Input Functions discussed on the following pages use these example addresses.

#### Input(n) Parameter Definitions

Parameter values are in Decimal format.

| Configured Function from        | Parameter 1 Contents        | Parameter 2 Contents         |

|---------------------------------|-----------------------------|------------------------------|

| CTRIO Workbench                 | DWORD                       | DWORD                        |

| Non-scaled Counter              | Raw Input Value             | Not Used                     |

| Scaled Counter                  | Scaled Value (pos. or rate) | Raw Value                    |

| Non-scaled Counter with Capture | Raw Value                   | Captured Value               |

| Scaled Counter with Capture     | Scaled Value (pos. or rate) | Scaled Captured Value        |

| Non-scaled Timer                | Previous Time (µs)          | In Progress Time (µs)        |

| Scaled Timer                    | Scaled Interval (rate)      | Scaled In Progress Time (µs) |

| Pulse Catch                     | Not Used                    | Not Used                     |

#### Counter & Quadrature Counter

Parameter 1 and 2 values, shown in the table above, will be mapped to V2000 - V2003 in this example. If input D is configured for Count Capture, the Enable Count Capture bit (see table below) must be ON in order for input D to be able to snapshot the current count. The Counter Capture Complete bit is used to indicate the acquisition has occurred. The program will need to turn OFF the Enable Capture and confirm the Capture Complete bit resets before attempting the next count capture. The Reset bit will reset raw and scaled values to the specified reset value. The last captured value, if applicable, will remain at V2054.

| Name                           | PLC Control<br>Outputs Base<br>Addr = V2030<br>(Bit-of-Word) | Addr = V2000 | PLC Control<br>Outputs Base<br>Addr = V2030<br>(Control Relay)<br>D2-240 | PLC Status<br>Inputs Base<br>Addr = V2000<br>(Control Relay)<br>D2-240 | Description                                                                                            |

|--------------------------------|--------------------------------------------------------------|--------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Parameter 1                    |                                                              | V2001-V2000  |                                                                          | V2001-V2000                                                            | Refer to table above                                                                                   |

| Parameter 2                    | N/A                                                          | V2003-V2002  | NI/A                                                                     | V2003-V2002                                                            | Refer to table above                                                                                   |

| Counter<br>Capture<br>Complete | IW/A                                                         | V2020.0      | N/A                                                                      | C160                                                                   | On when Count Capture is completed<br>(Available only when input D is<br>configured for Capture input) |

| Enable Count<br>Capture        | V2054.0                                                      | N/A          | C260                                                                     | N/A                                                                    | Turn ON to capture Count<br>(Available only when input D is<br>configured for Capture input)           |

| Reset                          | V2054.1                                                      |              | C261                                                                     |                                                                        | Turn ON to reset Counter Value to<br>Reset Value                                                       |

| At Reset<br>Value              | N/A                                                          | V2020.1      | N/A                                                                      | C161                                                                   | On when Counter is at Reset Value                                                                      |

**NOTE:** For **Direct**SOFT users: the I/O Map dialog displays the exact memory locations in use by the CTRIO(2) module. Within the I/O Map dialog you can print out a report of memory locations in use.

#### **Input Function Status Bit Definitions**

Input function offsets are listed in the order of Ch1/Fn1, Ch1/Fn2, Ch2/Fn1, Ch2/Fn2

| Ch(x)/Fn(x) Status Bits<br>(transfers from CTRIO(2) to CPU) | Bit Offsets: WinPLC, EBC, PBC, DEVNETS, MODBUS | V-memory Offsets<br><i>Direct</i> LOGIC PLCs |

|-------------------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Count Capture Complete Bit                                  | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

## Counter Function (IBoxes & DL-PLC

#### **Input Memory Map for Scaled Counter Data**

✓ DL ✓ Win

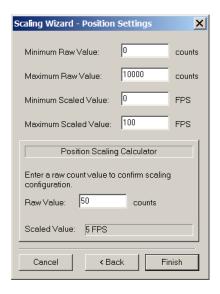

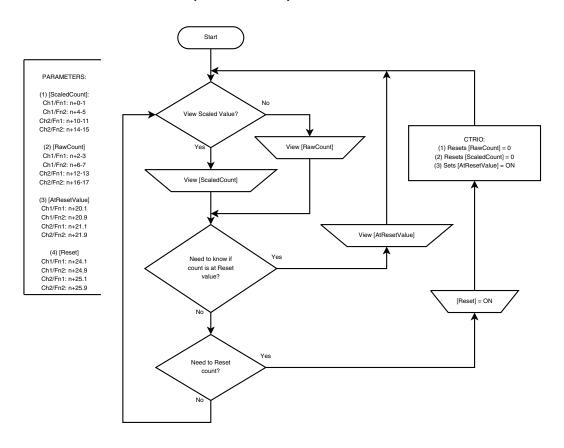

Scaled Counter is simply used to create counts in user-specified engineering units from an attached encoder. To use this function, one input needs to be configured as a Counter or Quad Counter. Then, for that Input functions, select the ruler icon and use the wizard to configure the desired engineering units.

This is the final panel in the Scaling Wizard. Be sure to use the Position Scaling Calculator to validate that the Raw Value (raw counts from the encoder) will generate the desired Scaled Value. Type in the test counts (50 is shown here) and verify the expected engineering units value is displayed in the Scaled Value field. It will be displayed with the Engineering Units characters provided earlier in the Wizard. FPS (feet per second) was used here. The Calculator returned '5FPS' here.

The following table shows which memory locations are used for memory transfers from the CTRIO(2) module to the CPU. The starting memory location is defined by the user in the I/O Map within CTRIO Workbench. When configuring the *Direct*LOGIC CPU, use the memory address offsets in the second column. When configuring an H2-WinPLC, EBC, PBC, MODBUS, or DEVNETS placed in the CPU slot, use the non-PLC offsets in column one.

| Data Type and Offset<br>WinPLC, EBC, PBC,<br>DEVNETS, MODBUS | Address for Inputs<br>( <i>Direct</i> LOGIC) | Definition                                                                                         | Format | Bytes |

|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-------|

| dwX0                                                         | n+0                                          | Ch 1/Fn 1 Parameter 1                                                                              |        |       |

| dwX1                                                         | n+2                                          | Ch 1/Fn 1 Parameter 2                                                                              |        |       |

| dwX2                                                         | n+4                                          | Ch 1/Fn 2 Parameter 1                                                                              |        |       |

| dwX3                                                         | n+6                                          | Ch 1/Fn 2 Parameter 2                                                                              | DWord  | 4     |

| dwX4                                                         | n+10                                         | Ch 2/Fn 1 Parameter 1                                                                              | Dvvoru | 4     |

| dwX5                                                         | n+12                                         | Ch 2/Fn 1 Parameter 2                                                                              |        |       |

| dwX6                                                         | n+14                                         | Ch 2/Fn 2 Parameter 1                                                                              |        |       |

| dwX7                                                         | n+16                                         | Ch 2/Fn 2 Parameter 2                                                                              |        |       |

| bX07<br>bX815                                                | n+20                                         | Ch 1/Fn 1 Status (Low Byte)<br>Ch 1/Fn 2 Status (High Byte)                                        |        |       |

| bX1623<br>bX2431                                             | n+21                                         | Ch 2/Fn 1 Status (Low Byte)<br>Ch 2/Fn 2 Status (High Byte)                                        | \\\d   | 0     |

| bX3239<br>bX4047                                             | n+22                                         | Output 0 Status (Low Byte)<br>Output 1 Status (High Byte)                                          | Word   | 2     |

| bX4855<br>bX5663                                             | n+23                                         | Output 2 Status (Low Byte)<br>Output 3 Status (High Byte)                                          |        |       |

| bX6471<br>bX7279<br>bX8087<br>bX8895                         | n+24                                         | System Functions<br>Read/Write CTRIO(2) Internal<br>Registers (see p. 6-10 for bit<br>definitions) | DWord  | 4     |

44 Total Bytes

#### Input(n) Parameter Definitions

Parameter values are in Decimal format.

| Configured Function from<br>CTRIO Workbench | Parameter 1 Contents DWORD  | Parameter 2 Contents<br>DWORD |

|---------------------------------------------|-----------------------------|-------------------------------|

| Non-scaled Counter                          | Raw Input Value             | Not Used                      |

| Scaled Counter                              | Scaled Value (pos. or rate) | Raw Value                     |

| Non-scaled Counter with Capture             | Raw Value                   | Captured Value                |

| Scaled Counter with Capture                 | Scaled Value (pos. or rate) | Scaled Captured Value         |

| Non-scaled Timer                            | Previous Time (µs)          | In Progress Time (μs)         |

| Scaled Timer                                | Scaled Interval (rate)      | Scaled In Progress Time (µs)  |

| Pulse Catch                                 | Not Used                    | Not Used                      |

#### Counter & Quadrature Counter

Parameters 1 and 2 are explained above and will be mapped to V2000 - V2003 in this example. If input D is configured for Count Capture, the Enable Count Capture bit must be ON in order for input D to be able to snapshot the current count. The Counter Capture Complete bit is used to indicate the acquisition has occurred. The program will need to turn OFF the Enable Capture and confirm the Capture Complete bit resets before attempting the next count capture. The Reset bit will reset raw and scaled values to the specified reset value. The last captured value, if applicable, will remain.

| Name                           | PLC Control<br>Outputs Base<br>Addr = V2030<br>(Bit-of-Word) | PLC Status<br>Inputs Base<br>Addr = V2000<br>(Bit-of-Word) | PLC Control<br>Outputs Base<br>Addr = V2030<br>(Control Relay)<br>D2-240 | PLC Status<br>Inputs Base<br>Addr = V2000<br>(Control Relay)<br>D2-240 | Description                                                                                            |

|--------------------------------|--------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Parameter 1                    |                                                              | V2001-V2000                                                |                                                                          | V2001-V2000                                                            | Refer to table above                                                                                   |

| Parameter 2                    | N/A                                                          | V2003-V2002                                                | NI/A                                                                     | V2003-V2002                                                            | Refer to table above                                                                                   |

| Counter<br>Capture<br>Complete | IWA                                                          | V2020.0                                                    | N/A                                                                      | C160                                                                   | On when Count Capture is completed<br>(Available only when input D is<br>configured for Capture input) |

| Enable Count<br>Capture        | V2054.0                                                      | N/A                                                        | C260                                                                     | N/A                                                                    | Turn ON to capture Count<br>(Available only when input D is<br>configured for Capture input)           |

| Reset                          | V2054.1                                                      |                                                            | C261                                                                     |                                                                        | Turn ON to reset Counter Value to<br>Reset Value                                                       |

| At Reset<br>Value              | N/A                                                          | V2020.1                                                    | N/A                                                                      | C161                                                                   | On when Counter is at Reset Value                                                                      |

**NOTE:** For **Direct**SOFT users: the **I/O Map** dialog displays the exact memory locations in use by the CTRIO(2) module. Within the I/O Map dialog you can print out a report of memory locations in use.

#### **Input Function Status Bit Definitions**

Input function offsets are listed in the order of Ch1/Fn1, Ch1/Fn2, Ch2/Fn1, Ch2/Fn2

| Ch(x)/Fn(x) Status Bits<br>(Transfers from CTRIO(2) to CPU) | Bit Offsets: WinPLC, EBC, PBC, DEVNETS, MODBUS | V-memory Offsets<br><i>Direct</i> LOGIC PLCs |

|-------------------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Count Capture Complete Bit                                  | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

#### Counter Function (Scaled) (IBoxes & DL-PLC)

## DL Win

#### **Input Memory Map for Capture Count Data Transfers**

This function copies the current value of a counter input into a register when a discrete input trigger condition is met. To use this function, one input must be configured as a Counter or Quad Counter and one as Capture Fn. An input must be set as a counter before Capture Fn will appear in the menu of CTRIO Workbench dialog box.

The following table shows which memory locations are used for memory transfers from the CTRIO(2) module to the CPU. The starting memory location is defined by the user in the I/O Map within CTRIO Workbench. When configuring the *Direct*LOGIC CPU, use the memory address offsets in the second column. When configuring an H2-WinPLC, EBC, PBC, MODBUS, or DEVNETS placed in the CPU slot, use the non-PLC offsets in column one.

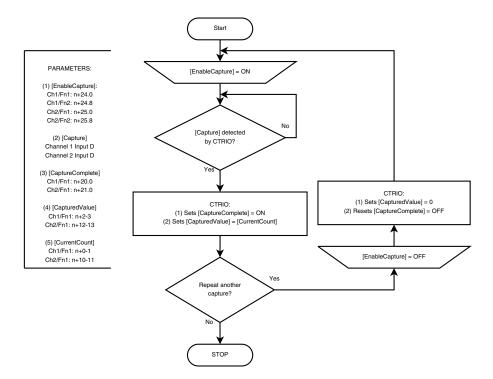

The proper sequence of events for using this function can be found in the flow charts on the pages that follow.

| Data Type and Offset<br>WinPLC, EBC, PBC,<br>DEVNETS, MODBUS | Address for Inputs<br>( <i>Direct</i> LOGIC) | Definition                                                                                         | Format | Bytes |

|--------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-------|

| dwX0                                                         | n+0                                          | Ch 1/Fn 1 Parameter 1                                                                              |        |       |

| dwX1                                                         | n+2                                          | Ch 1/Fn 1 Parameter 2                                                                              |        |       |

| dwX2                                                         | n+4                                          | Ch 1/Fn 2 Parameter 1                                                                              |        |       |

| dwX3                                                         | n+6                                          | Ch 1/Fn 2 Parameter 2                                                                              | DWord  | 4     |

| dwX4                                                         | n+10                                         | Ch 2/Fn 1 Parameter 1                                                                              | Dvvora | 4     |

| dwX5                                                         | n+12                                         | Ch 2/Fn 1 Parameter 2                                                                              |        |       |

| dwX6                                                         | n+14                                         | Ch 2/Fn 2 Parameter 1                                                                              |        |       |

| dwX7                                                         | n+16                                         | Ch 2/Fn 2 Parameter 2                                                                              |        |       |

| bX07<br>bX815                                                | n+20                                         | Ch 1/Fn 1 Status (Low Byte)<br>Ch 1/Fn 2 Status (High Byte)                                        |        |       |

| bX1623<br>bX2431                                             | n+21                                         | Ch 2/Fn 1 Status (Low Byte)<br>Ch 2/Fn 2 Status (High Byte)                                        | Mand   | 0     |

| bX3239<br>bX4047                                             | n+22                                         | Output 0 Status (Low Byte)<br>Output 1 Status (High Byte)                                          | Word   | 2     |

| bX4855<br>bX5663                                             | n+23                                         | Output 2 Status (Low Byte)<br>Output 3 Status (High Byte)                                          |        |       |

| bX6471<br>bX7279<br>bX8087<br>bX8895                         | n+24                                         | System Functions<br>Read/Write CTRIO(2) Internal<br>Registers (see p. 6-10 for bit<br>definitions) | DWord  | 4     |

44 Total Bytes

#### Input(n) Parameter Definitions

Parameter values are in Decimal format.

| Configured Function from        | Parameter 1 Contents        | Parameter 2 Contents         |

|---------------------------------|-----------------------------|------------------------------|

| CTRIO Workbench                 | DWORD                       | DWORD                        |

| Non-scaled Counter              | Raw Input Value             | Not Used                     |

| Scaled Counter                  | Scaled Value (pos. or rate) | Raw Value                    |

| Non-scaled Counter with Capture | Raw Value                   | Captured Value               |

| Scaled Counter with Capture     | Scaled Value (pos. or rate) | Scaled Captured Value        |

| Non-scaled Timer                | Previous Time (µs)          | In Progress Time (µs)        |

| Scaled Timer                    | Scaled Interval (rate)      | Scaled In Progress Time (µs) |

| Pulse Catch                     | Not Used                    | Not Used                     |

**NOTE:** For **Direct**SOFT users: the **I/O Map** dialog displays the exact memory locations in use by the CTRIO(2) module. Within the I/O Map dialog you can print out a report of memory locations in use.

#### **Input Function Status Bit Definitions**

Input function offsets are listed in the order of Ch1/Fn1, Ch1/Fn2, Ch2/Fn1, Ch2/Fn2

| Ch(x)/Fn(x) Status Bits<br>(Transfers from CTRIO(2) to CPU)  | Bit Offsets: WinPLC, EBC, PBC, DEVNETS, MODBUS | V-memory Offsets<br><i>Direct</i> LOGIC PLCs |

|--------------------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Count Capture Complete Bit                                   | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Timer Capture Start                                          | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Timer Capture Complete (Timing) OR At Reset Value (Counting) | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

| Timer "Timed Out" Bit                                        | 2, 10, 18, 26                                  | 20.2, 20.10, 21.2, 21.10                     |

| Pulse Catch Output Pulse State                               | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Pulse Catch Start                                            | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

## Capture Count Function (IBoxes & DL-PLC)

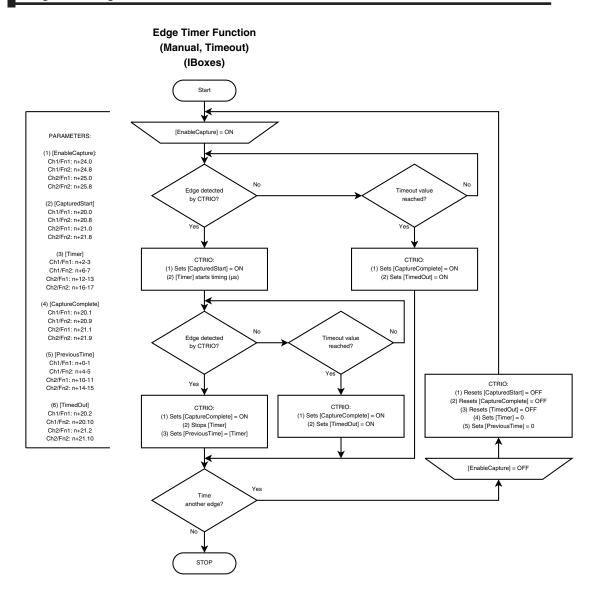

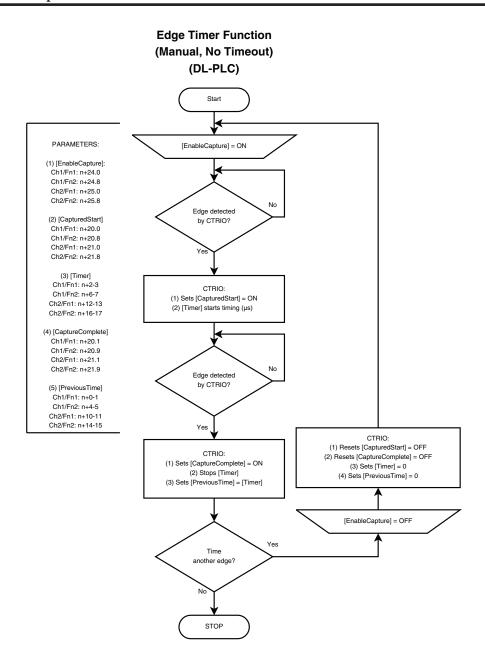

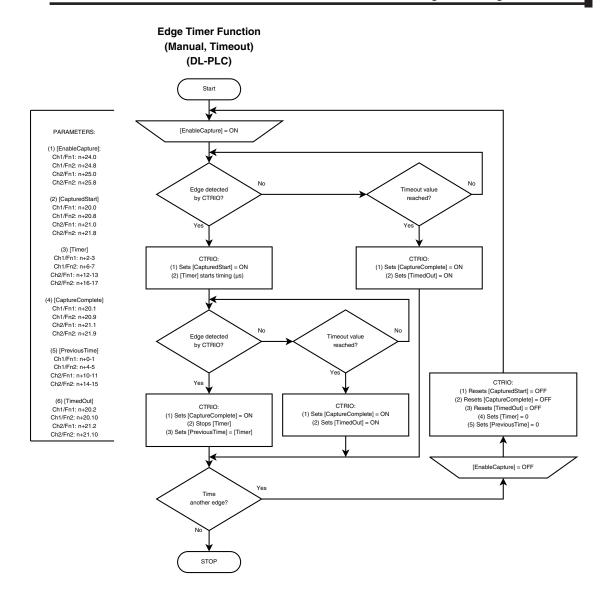

### Input Memory Map for Edge Timer and **Dual Edge Timer**

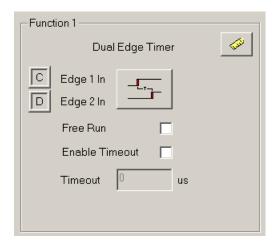

Edge Timer and Dual Edge Timer are used to precisely measure the time between two discrete input events. To use one of these functions, configure one input as Edge Timer or configure two inputs as Dual Edge Timer. Then cycle through the various edge options by repeatedly pressing the button with the graphic depiction of the signal edges.

Function one shows the configuration for a Dual Edge Timer that will time from the rising edge of Input C to the rising edge of Input D. Free Run is not selected and Enable Timeout is not selected. There is no scaling. If Scaling were selected, the time result would be in the selected engineering units.

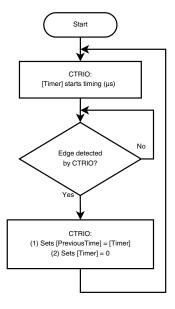

Running an Edge Timer with the default settings takes the least supporting code to operate. The default settings are Free Run disabled and Enable Timeout disabled.

When Free Run is enabled, the timer will start as soon as Edge 1 In is true. With Free Run enabled, the timer will always show the last valid capture value; or, 0 if the last measurement resulted in a timeout.

When Free Run is disabled, the timer will start when Enable Capture and Edge 1 are true. With Free Run disabled, the timer will show the last time captured.

When Enable Timeout is enabled, the timer will timeout if the Edge 2 event does not occur before the timeout timer expires. The timeout timer starts when Enable Capture is true and Edge 1 becomes true. When a timeout occurs, the Timeout and Capture Complete bit are set and the Timer and Last Time values are cleared.

When Enable Timeout is disabled, once Edge 1 event is true, the timer will run until Edge 2 event becomes true.

The behavior resulting from various combinations of the options above can also be found in the flow charts that follow.

The following table shows which memory locations are used for memory transfers from the CTRIO(2) module to the CPU. The starting memory location is defined by the user in the I/O Map within CTRIO Workbench. When configuring the *Direct*LOGIC CPU, use the memory address offsets in the second column. When configuring an H2-WinPLC, EBC, PBC, MODBUS, or DEVNETS placed in the CPU slot, use the non-PLC offsets in column one.

| Data Type and Offset<br>WinPLC, EBC, PBC,<br>DEVNETS, MODBUS | Address for Inputs<br>( <i>Direct</i> LOGIC)                | Definition                                                                                         | Format | Bytes |

|--------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------|-------|

| dwX0                                                         | n+0                                                         | Ch 1/Fn 1 Parameter 1                                                                              |        |       |

| dwX1                                                         | n+2                                                         | Ch 1/Fn 1 Parameter 2                                                                              |        |       |

| dwX2                                                         | n+4                                                         | Ch 1/Fn 2 Parameter 1                                                                              |        |       |

| dwX3                                                         | n+6                                                         | Ch 1/Fn 2 Parameter 2                                                                              | DWord  | 4     |

| dwX4                                                         | n+10                                                        | Ch 2/Fn 1 Parameter 1                                                                              | DVVora | 4     |

| dwX5                                                         | n+12                                                        | Ch 2/Fn 1 Parameter 2                                                                              |        |       |

| dwX6                                                         | n+14                                                        | Ch 2/Fn 2 Parameter 1                                                                              |        |       |

| dwX7                                                         | n+16                                                        | Ch 2/Fn 2 Parameter 2                                                                              |        | İ     |

| bX07<br>bX815                                                | n+20                                                        | Ch 1/Fn 1 Status (Low Byte)<br>Ch 1/Fn 2 Status (High Byte)                                        |        |       |

| bX1623<br>bX2431                                             | n+21                                                        | Ch 2/Fn 1 Status (Low Byte)<br>Ch 2/Fn 2 Status (High Byte)                                        | 10/ad  | 0     |

| bX3239<br>bX4047                                             | n+22 Output 0 Status (Low Byte) Output 1 Status (High Byte) |                                                                                                    | Word   | 2     |

| bX4855<br>bX5663                                             | n+23                                                        | Output 2 Status (Low Byte)<br>Output 3 Status (High Byte)                                          |        |       |

| bX6471<br>bX7279<br>bX8087<br>bX8895                         | n+24                                                        | System Functions<br>Read/Write CTRIO(2) Internal<br>Registers (see p. 6-10 for bit<br>definitions) | DWord  | 4     |

44 Total Bytes

#### Input(n) Parameter Definitions

Parameter values are in Decimal format.

| Configured Function from    | Parameter 1 Contents        | Parameter 2 Contents         |

|-----------------------------|-----------------------------|------------------------------|

| CTRIO Workbench             | DWORD                       | DWORD                        |

| Scaled Counter with Capture | Scaled Value (pos. or rate) | Scaled Captured Value        |

| Non-scaled Timer            | Previous Time (µs)          | In Progress Time (μs)        |

| Scaled Timer                | Scaled Interval (rate)      | Scaled In Progress Time (µs) |

#### Input(n) Parameter Edge Timer and Dual Edge Timer

Parameters 1 and 2 are explained and will be mapped to V2000 - V2003 in this example.

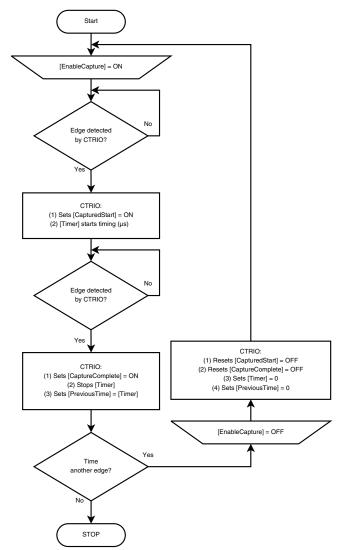

#### Standard Timers:

When the Enable Timer Capture bit is ON and the configured input edge occurs, the CTRIO(2) module will begin timing. The Timer Capture Starting bit will be ON while the timing is in progress and will turn OFF when the next configured input edge occurs and the Timer Capture Complete bit turns ON. The program will need to turn off the Enable Timer Capture bit, and confirm the Timer Capture Starting and Timer Capture Complete bits reset before attempting the next time capture cycle. Turning OFF the Enable Timer Capture bit resets the timers register values to zero.

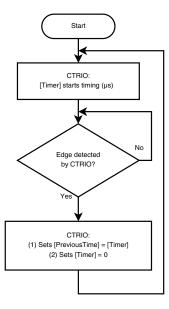

#### Free Run Timers:

If the Free Run Timer option was configured, the Enable Timer Capture bit is not available. When the configured input edge occurs, the CTRIO(2) module will begin timing. The Timer Capture Starting bit will be ON while the timing is in progress and will turn OFF when the next configured input edge occurs. When this edge occurs, the Timer "in progress time" register resets to zero. The "previous time" register will always retain the most recent captured time value.

| Name                         | PLC Control<br>Outputs Base<br>Addr = V2030<br>(Bit-of-Word) | PLC Status<br>Inputs Base<br>Addr = V2000<br>(Bit-of-Word) | PLC Control<br>Outputs Base<br>Addr = V2030<br>(Control Relay)<br>D2-240 | PLCStatus<br>Inputs Base<br>Addr = V2000<br>(Control Relay)<br>D2-240 | Description                                                                                           |

|------------------------------|--------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Parameter 1                  |                                                              | V2001-V2000                                                |                                                                          | V2001-V2000                                                           | Previous Time                                                                                         |

| Parameter 2                  | N/A                                                          | V2003-V2002                                                | N/A                                                                      | V2003-V2002                                                           | In Progress Time                                                                                      |

| Timer<br>Capture<br>Starting |                                                              | V2020.0                                                    |                                                                          | C160                                                                  | On when Time Capture is in progress                                                                   |

| Enable Timer<br>Capture      | V2054.0                                                      | N/A                                                        | C260                                                                     | N/A                                                                   | Turn ON to enable Timer Capture<br>Function (Not available when Free<br>Run Timer option is selected) |

| Timer<br>Capture<br>Complete | N/A                                                          | V2020.1                                                    | N/A                                                                      | C161                                                                  | On when Timing is completed                                                                           |

| Timer<br>Timeout Bit         | IW/A                                                         | V2020.2                                                    | IV/A                                                                     | C162                                                                  | Set when Timeout Occurs                                                                               |

#### **Edge and Dual Edge Timer Timeout Function**

The Timer Timeout Function is available for use with standard and Free Run Timers. It is primarily used in Free Run timing of recurring events (rate, velocity calculations, etc.). The specified Timeout Period is in effect once the timer is enabled until receiving the first configured input edge. Then it is in effect until receiving the next edge of the timing input to complete the timing cycle.

#### Standard Timers:

Once the timer is enabled, the Timeout Bit is set if the time that it takes the CTRIO(2) module to see the configured input edge exceeds the specified Timeout Period. The program will need to turn off the Enable Timer Capture bit, and confirm the Timer Capture Complete bit and Timeout bit resets before attempting the next time capture cycle.

Once timing has been initiated, if the time before the CTRIO(2) module sees the next configured edge exceeds the specified Timeout Period, the Timeout bit is set. The Timer register values are reset to zero. The program will need to turn off the Enable Timer Capture bit, and confirm the Timer Capture Starting bit, Timer Capture Complete bit and the Timeout bit reset before attempting the next time capture cycle.

#### Free Run Timers:

The Timeout Bit is set if the time that it takes the CTRIO(2) module to see the configured input edge exceeds the specified Timeout Period. The Timeout bit resets when the next timing cycle begins. The "Previous Time" register value is reset to zero.

Once timing has been initiated, if the time before the CTRIO(2) module sees the next configured edge exceeds the specified Timeout Period, the Timeout bit is set. The Timer register values are reset to zero. The Timeout bit resets when the next timing cycle begins.

**NOTE:** For **Direct**SOFT users: the **I/O Map** dialog displays the exact memory locations in use by the CTRIO(2) module. Within the I/O Map dialog you can print out a report of memory loctions in use.

#### **Input Function Status Bit Definitions**

Input function offsets are listed in the order of Ch1/Fn1, Ch1/Fn2, Ch2/Fn1, Ch2/Fn2

| Ch(x)/Fn(x) Status Bits<br>(Transfers from CTRIO(2) to CPU)     | Bit Offsets: WinPLC, EBC, PBC, DEVNETS, MODBUS | V-memory Offsets<br><i>Direct</i> LOGIC PLCs |

|-----------------------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Count Capture Complete Bit                                      | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Timer Capture Start                                             | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Timer Capture Complete (Timing) OR<br>At Reset Value (Counting) | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

| Timer "Timed Out" Bit                                           | 2, 10, 18, 26                                  | 20.2, 20.10, 21.2, 21.10                     |

| Pulse Catch Output Pulse State                                  | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Pulse Catch Start                                               | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

#### **Edge Timer Function** (Free Run, Timeout) (IBoxes)

#### PARAMETERS:

(1) [Timer] Ch1/Fn1: n+2-3 Ch1/Fn2: n+6-7 Ch2/Fn1: n+12-13 Ch2/Fn2: n+16-17

(2) [PreviousTime] Ch1/Fn1: n+0-1 Ch1/Fn2: n+4-5 Ch2/Fn1: n+10-11 Ch2/Fn2: n+14-15

(3) [TimedOut] Ch1/Fn1: n+20.2 Ch1/Fn2: n+20.10 Ch2/Fn1: n+21.2 Ch2/Fn2: n+21.10

#### **Edge Timer Function** (Free Run, No Timeout) (IBoxes)

#### PARAMETERS:

(1) [Timer] Ch1/Fn1: n+2-3 Ch1/Fn2: n+6-7 Ch2/Fn1: n+12-13 Ch2/Fn2: n+16-17

Ch1/Fn1: n+0-1 Ch1/Fn2: n+4-5 Ch2/Fn1: n+10-11 Ch2/Fn2: n+14-15

(2) [PreviousTime]

#### Edge Timer Function (Manual, No Timeout) (IBoxes)

#### PARAMETERS:

- (1) [EnableCapture]: Ch1/Fn1: n+24.0 Ch1/Fn2: n+24.8 Ch2/Fn1: n+25.0 Ch2/Fn2: n+25.8

- (2) [CapturedStart] Ch1/Fn1: n+20.0 Ch1/Fn2: n+20.8 Ch2/Fn1: n+21.0 Ch2/Fn2: n+21.8

- (3) [Timer] Ch1/Fn1: n+2-3 Ch1/Fn2: n+6-7 Ch2/Fn1: n+12-13 Ch2/Fn2: n+16-17

- (4) [CaptureComplete] Ch1/Fn1: n+20.1 Ch1/Fn2: n+20.9 Ch2/Fn1: n+21.1 Ch2/Fn2: n+21.9

- (5) [PreviousTime] Ch1/Fn1: n+0-1 Ch1/Fn2: n+4-5 Ch2/Fn1: n+10-11 Ch2/Fn2: n+14-15

## PARAMETERS: (1) [Timer] (2) [PreviousTime] (Chilfent : n-0-1 (2) [PreviousTime] (Chilfent : n-0-1 (Chilfent : n-0-1 (Chilfent : n-0-1 (Dhilfent : n-0-1 (D

Ch1/Fn1: n+0-1 Ch1/Fn2: n+4-5 Ch2/Fn1: n+10-11 Ch2/Fn2: n+14-15

(3) [TimedOut] Ch1/Fn1: n+20.2 Ch1/Fn2: n+20.10 Ch2/Fn1: n+21.2 Ch2/Fn2: n+21.10

#### Edge Timer Function (Free Run, No Timeout) (DL-PLC)

PARAMETERS:

(1) [Timer]

Ch1/Fn1: n+2-3

Ch1/Fn2: n+6-7

Ch2/Fn1: n+12-13

Ch2/Fn2: n+16-17

(2) [PreviousTime]

Ch1/Fn1: n+0-1

Ch1/Fn2: n+4-5

Ch2/Fn1: n+10-11

Ch2/Fn2: n+14-15

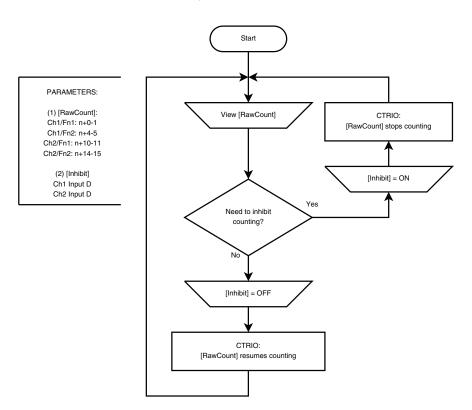

#### **Inhibit**

✓ DL ✓ Win

Inhibit allows an input of the CTRIO(2) to pause the counting of Function 1, a Quad Counter or simple Counter. To use this function, Input A must be configured as a Counter or Quad Counter. An input must be set as a counter before Inhibit Fn 1 will appear in the menu in CTRIO Workbench.

The following table shows which memory locations are used for memory transfers from the CTRIO(2) module to the CPU. The starting memory location is defined by the user in the I/O Map within CTRIO Workbench. When configuring the *Direct*LOGIC CPU, use the memory address offsets in the second column. When configuring an H2-WinPLC, EBC, PBC, MODBUS, or DEVNETS placed in the CPU slot, use the non-PLC offsets in column one.

| Data Type and Offset<br>WinPLC, EBC, PBC,<br>DEVNETS, MODBUS | Address for Inputs<br>( <i>Direct</i> LOGIC)                     | Definition                                                                                | Format             | Bytes |

|--------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|-------|

| dwX0                                                         | n+0                                                              | Ch 1/Fn 1 Parameter 1                                                                     | 1/Fn 1 Parameter 1 |       |

| dwX1                                                         | n+2                                                              | Ch 1/Fn 1 Parameter 2                                                                     |                    |       |

| dwX2                                                         | n+4                                                              | Ch 1/Fn 2 Parameter 1                                                                     |                    |       |

| dwX3                                                         | n+6                                                              | Ch 1/Fn 2 Parameter 2                                                                     | DWord              | 4     |

| dwX4                                                         | n+10                                                             | Ch 2/Fn 1 Parameter 1                                                                     | DVVOIU             | 4     |

| dwX5                                                         | n+12                                                             | Ch 2/Fn 1 Parameter 2                                                                     |                    |       |

| dwX6                                                         | n+14                                                             | Ch 2/Fn 2 Parameter 1                                                                     |                    |       |

| dwX7                                                         | n+16                                                             | Ch 2/Fn 2 Parameter 2                                                                     |                    |       |

| bX07<br>bX815                                                | n+20                                                             | Ch 1/Fn 1 Status (Low Byte)<br>Ch 1/Fn 2 Status (High Byte)                               |                    |       |

| bX1623<br>bX2431                                             | n+21 Ch 2/Fn 1 Status (Low Byte)<br>Ch 2/Fn 2 Status (High Byte) |                                                                                           | Word               | 0     |

| bX3239<br>bX4047                                             | n+22 Output 0 Status (Low Byte) Output 1 Status (High Byte)      |                                                                                           | vvora              | 2     |

| bX4855<br>bX5663                                             | n+23                                                             | Output 2 Status (Low Byte)<br>Output 3 Status (High Byte)                                 |                    |       |

| bX6471<br>bX7279<br>bX8087<br>bX8895                         | n+24                                                             | System Functions Read/Write CTRIO(2) Internal Registers (see p. 6-10 for bit definitions) |                    | 4     |

44 Total Bytes

#### Input (n) Parameter Definitions

Parameter values are in Decimal format.

| Configured Function from        | Parameter 1 Contents        | Parameter 2 Contents         |

|---------------------------------|-----------------------------|------------------------------|

| CTRIO Workbench                 | DWORD                       | DWORD                        |

| Non-scaled Counter              | Raw Input Value             | Not Used                     |

| Scaled Counter                  | Scaled Value (pos. or rate) | Raw Value                    |

| Non-scaled Counter with Capture | Raw Value                   | Captured Value               |

| Scaled Counter with Capture     | Scaled Value (pos. or rate) | Scaled Captured Value        |

| Non-scaled Timer                | Previous Time (µs)          | In Progress Time (μs)        |

| Scaled Timer                    | Scaled Interval (rate)      | Scaled In Progress Time (µs) |

| Pulse Catch                     | Not Used                    | Not Used                     |

**NOTE:** For **Direct**SOFT users: the **I/O Map** dialog displays the exact memory locations in use by the CTRIO(2) module. Within the I/O Map dialog you can print out a report of memory locations in use.

#### **Input Function Status Bit Definitions**

Input function offsets are listed in the order of Ch1/Fn1, Ch1/Fn2, Ch2/Fn1, Ch2/Fn2

| Ch(x)/Fn(x) Status Bits<br>(Transfers from CTRIO(2) to CPU)  | Bit Offsets: WinPLC, EBC, PBC, DEVNETS, MODBUS | V-memory Offsets<br><i>Direct</i> LOGIC PLCs |

|--------------------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Count Capture Complete Bit                                   | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Timer Capture Start                                          | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Timer Capture Complete (Timing) OR At Reset Value (Counting) | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

| Timer "Timed Out" Bit                                        | 2, 10, 18, 26                                  | 20.2, 20.10, 21.2, 21.10                     |

| Pulse Catch Output Pulse State                               | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Pulse Catch Start                                            | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

## Inhibit Function (IBoxes & DL-PLC

### ✓ DL ✓ Win

#### put Memory Map for Pulse Catch Data Transfers

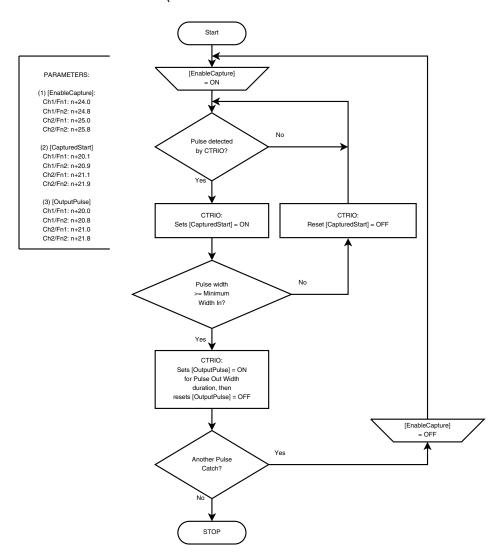

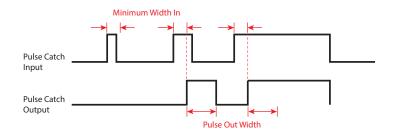

The Pulse Catch function allows a very short duration pulse to be qualified and lengthened to a time period long enough to guarantee that it is seen by the CPU. CPU scans necessarily vary with the length and complexity of the user's program. A scan frequency of several milliseconds is possible. On a conventional discrete input module, if a pulse is shorter than one scan time, there is a chance the CPU will not see the pulse.

The CTRIO(2) module's Pulse Catch function sees the fast incoming signal and holds its

status in a status bit until the CPU can see it. A discrete output(s) can also be tied to follow the Pulse Catch.

Notice that the module's four input terminals are represented by the A, B, C, and D boxes on the left side of this dialog. When wiring an input to terminal 1C, select the Channel 1 tab near the top of this window and click Pulse Catch in box C.

Three selections must be made in conjunction with the Pulse Catch option.

1. Choose the rising edge of the pulse or the falling edge of the pulse. This is a critical decision. Careful attention should be paid to the type of output the field

- device generates. If the signal voltage is normally low, but a short duration pulse sends the signal to the ON state, you will want to trigger off the rising edge, and vice versa.

- 2. Enter the minimum pulse width to capture. Transients below this width will not be recorded. Set this value by typing the desired value in the "Minimum Width In" field.

- 3. Enter the minimum length of pulse the CTRIO(2) module should send in response to the input pulse. Make this setting by typing in the desired value in the "Pulse Out Width" field.

The following table shows which memory locations are used for memory transfers from the CTRIO(2) module to the CPU. The starting memory location is defined by the user in the I/O Map within CTRIO Workbench. When you are using the *Direct*LOGIC CPU, use the memory address offsets in the second column. When using an H2-WinPLC, EBC, PBC, MODBUS, or DEVNETS in the CPU slot, use the non-PLC offsets in column one.

| Data Type and Offset<br>WinPLC, EBC, PBC,<br>DEVNETS, MODBUS | Address for Inputs<br>( <i>Direct</i> LOGIC)                     | Definition                                                                                       | Format | Bytes |

|--------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|-------|

| dwX0                                                         | n+0                                                              | Ch 1/Fn 1 Parameter 1                                                                            |        |       |

| dwX1                                                         | n+2                                                              | Ch 1/Fn 1 Parameter 2                                                                            |        |       |

| dwX2                                                         | n+4                                                              | Ch 1/Fn 2 Parameter 1                                                                            |        |       |

| dwX3                                                         | n+6                                                              | Ch 1/Fn 2 Parameter 2                                                                            | DWord  | 4     |

| dwX4                                                         | n+10                                                             | Ch 2/Fn 1 Parameter 1                                                                            | Dvvora | 4     |

| dwX5                                                         | n+12                                                             | Ch 2/Fn 1 Parameter 2                                                                            |        |       |

| dwX6                                                         | n+14                                                             | Ch 2/Fn 2 Parameter 1                                                                            |        |       |

| dwX7                                                         | n+16                                                             | Ch 2/Fn 2 Parameter 2                                                                            |        |       |

| bX07<br>bX815                                                | n+20                                                             | Ch 1/Fn 1 Status (Low Byte)<br>Ch 1/Fn 2 Status (High Byte)                                      | ` ,    |       |

| bX1623<br>bX2431                                             | n+21 Ch 2/Fn 1 Status (Low Byte)<br>Ch 2/Fn 2 Status (High Byte) |                                                                                                  | Word   | 2     |

| bX3239<br>bX4047                                             | n+22                                                             | Output 0 Status (Low Byte)                                                                       |        | 2     |

| bX4855<br>bX5663                                             | n+23                                                             | Output 2 Status (Low Byte)<br>Output 3 Status (High Byte)                                        |        |       |

| bX6471<br>bX7279<br>bX8087<br>bX8895                         | n+24                                                             | System Functions Read/Write CTRIO(2) Internal Registers (see p. 6-10 for bit definitions)  DWord |        | 4     |

44 Total Bytes

#### Input (n) Parameter Definitions

Parameter values are in Decimal format.

| Configured Function from        | Parameter 1 Contents        | Parameter 2 Contents         |

|---------------------------------|-----------------------------|------------------------------|

| CTRIO Workbench                 | DWORD                       | DWORD                        |

| Non-scaled Counter              | Raw Input Value             | Not Used                     |

| Scaled Counter                  | Scaled Value (pos. or rate) | Raw Value                    |

| Non-scaled Counter with Capture | Raw Value                   | Captured Value               |

| Scaled Counter with Capture     | Scaled Value (pos. or rate) | Scaled Captured Value        |

| Non-scaled Timer                | Previous Time (µs)          | In Progress Time (μs)        |

| Scaled Timer                    | Scaled Interval (rate)      | Scaled In Progress Time (µs) |

| Pulse Catch                     | Not Used                    | Not Used                     |

**NOTE:** For **Direct**SOFT users: the **I/O Map** dialog displays the exact memory locations in use by the CTRIO(2) module. Within the I/O Map dialog you can print out a report of memory locations in use.

#### **Input Function Status Bit Definitions**

Input function offsets are listed in the order of Ch1/Fn1, Ch1/Fn2, Ch2/Fn1, Ch2/Fn2

| Ch(x)/Fn(x) Status Bits<br>(Transfers from CTRIO(2) to CPU) | Bit Offsets: WinPLC, EBC, PBC, DEVNETS, MODBUS | V-memory Offsets<br><i>Direct</i> LOGIC PLCs |

|-------------------------------------------------------------|------------------------------------------------|----------------------------------------------|

| Pulse Catch Output Pulse State                              | 0, 8, 16, 24                                   | 20.0, 20.8, 21.0, 21.8                       |

| Pulse Catch Start                                           | 1, 9, 17, 25                                   | 20.1, 20.9, 21.1, 21.9                       |

#### **Pulse Catch Function** (IBoxes & DL-PLC