|

|

Topic: P303 |

P1-PWM |

|

|

|

Topic: P303 |

P1-PWM |

|

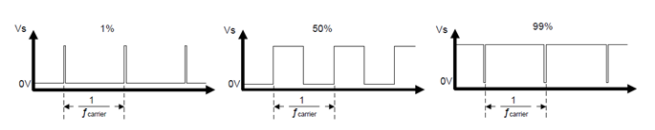

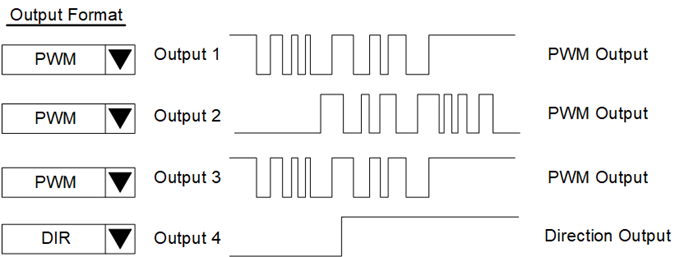

A Pulse Width Modulation (PWM) Signal is a method for generating an analog signal using a digital source. A PWM signal consists of two main components that define its behavior: a duty cycle and a frequency. The duty cycle describes the amount of time the signal is in a high (on) state as a percentage of the total time of it takes to complete one cycle. The frequency determines how fast the PWM completes a cycle (i.e. 1000 Hz would be 1000 cycles per second), and therefore how fast it switches between high and low states. By cycling a digital signal off and on at a fast enough rate, and with a certain duty cycle, the output will appear to behave like a constant voltage analog signal when providing power to devices.

Note: Invert the signal by simply using the sinking outputs or use a MATH instruction to produce it in ladder such as DCINVERTED=100-DCCOMMAND.

|

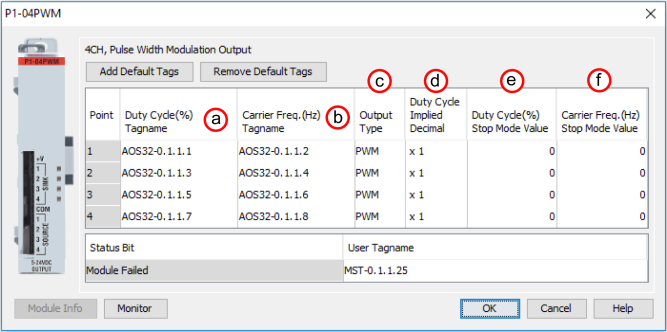

Selection / Data Range |

Notes |

|

x 1 |

* - Duty Cycle Range 0 -> 100 |

|

x 0.1 |

* - Duty Cycle Range 0 -> 1000 |

|

x 0.01 |

* - Duty Cycle Range 0 -> 10000 |

Duty Cycle Stop Mode Value: This is the value written to the duty cycle when the CPU goes into Stop Mode.

Note: Raw, unscaled value. Does not consider Implied Decimal.

Carrier Frequency Stop Mode Value: This is the value written to the Carrier Frequency when the CPU goes into Stop Mode.